MS thesis defense

A Fast Fullchip Transient Response Estimation Technique

Sushmita K. Rao

11:00am Monday, 25 July 2011, ITE 346

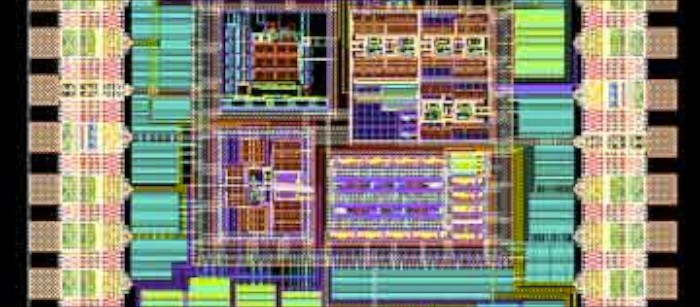

Circuit Simulation has long been a dependable technique for design engineers for functional testing before a circuit is taken to silicon. But as we move into very deep sub-micron technologies, chips are becoming more complex and denser. The dense power grid adds to long simulation run time rendering fullchip simulations difficult and computationally expensive for larger designs. Some large designs may not be simulatable owing to system requirements. Even fast simulators like Cadence UltraSim fail to provide SPICE level accuracy. Dynamic solutions provide greater accuracy than statistical techniques but long simulation run time becomes the biggest tradeoff. Accurate measurement of dynamic currents is required for applications like power estimation, supply noise predictions and in verifying the power grid designs and testing. The research reported in this thesis is focussed on providing a current based method to estimate a fullchip's transient response without carrying out a fullchip simulation. Instead, a part of the chip is simulated and the power port currents thus measured are used to estimate the fullchip currents using the principle of superposition. This technique eliminates fullchip simulations that are complex and time consuming but the accuracy is maintained as the fullchip estimation is carried out on simulated data. A simple scaling method is also proposed to compensate for resistive variations in the test circuits. Experimental results reported demonstrate the effectiveness of the method.

Committee members:

- Dr. Chintan Patel (Chair)

- Dr. Ryan Robucci

- Dr. Tinoosh Mohsenin