Ph.D. Dissertation Defense

Computer Engineering

PSANDE: A Framework for Accurate Dynamic

Power Supply Analysis and Delay Estimation

Sushmita K. Rao

11:30am Friday, 3 April 2015, ITE 325b, UMBC

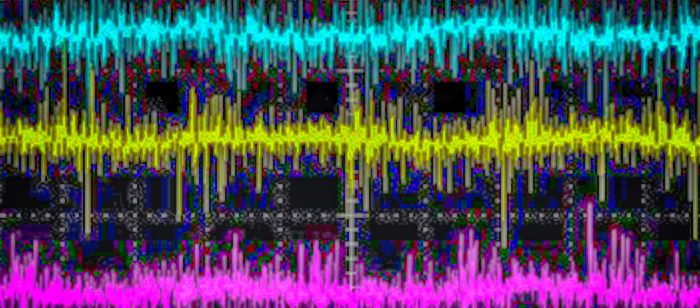

Power-supply noise is a major contributing factor for yield loss in sub-micron designs. Excessive switching in test mode causes supply voltage to droop more than in functional mode, leading to failures in delay tests that would not occur otherwise under normal operation. There exists a need to accurately estimate on-chip supply noise early in the design phase to meet power requirements in normal mode and during test to prevent over-stimulation during testing and avoid false failures. Simultaneous switching activity (SSA) of several logic components is one of the main sources of power-supply noise (PSN) which results in reduction of supply voltages at the power-supplies of the logic gates. Current research concentrates on static IR-drop, which accounts for only part of the total voltage drop on the power grid and therefore is insufficient for nanometer designs. Inductive drop is not included in current noise analysis techniques for simplification.

The power delivery networks in today’s very deep-submicron chips are susceptible to slight variations and cause sudden large current spikes leading to higher Ldi/dt drop than resistive drop, necessitating the need to be accounted. Especially of concern is simultaneous switching in localized areas in a chip because it concentrates current drawn on a particular power bump further reducing supply voltage. Thus, there arises a growing need to accurately characterize the resistive and inductive voltage drop caused by simultaneous switching of multiple paths. Power-supply noise also impacts circuit operation, causing a significant increase in path delays. It is critical to account for this increase in delay during the ATPG process otherwise it can lead to overkill during transition and delay testing. However, it is infeasible to carry out full-chip SPICE-level simulations on a design to validate the large number of ATPG generated test patterns. Accurate and efficient techniques are required to quantify supply noise and its impact on path delays to ensure reliable operation in both mission mode and during test.

A scalable current-based dynamic method is presented to estimate both IR and Ldi/dt drop caused by simultaneous switching activity. Also presented is a technique to predict the increase in path delays caused by supply noise. The noise and delay estimation techniques use simulations of individual extracted switching logic in comparison to time-consuming full-chip simulations and thus it can be integrated with existing ATPG tools. A design partitioning technique is also presented that makes the framework feasible for larger designs. Supply noise estimation error is less than 12% of SPICE level full-chip results across all test cases in the combinational and sequential benchmark circuits. The effect of power supply noise on path delays is modeled effectively. Results from multiple designs show that using the convolution-based technique the increase in path delay can be accurately predicted with a worst case error of 4% as compared to full-chip simulation results demonstrating the effectiveness of the technique.

Committee: Drs. Chintan Patel (Chair), Dhananjay Phatak, Ryan Robucci, Nilanjan Banerjee and Ismed Hartanto (Xilinx)